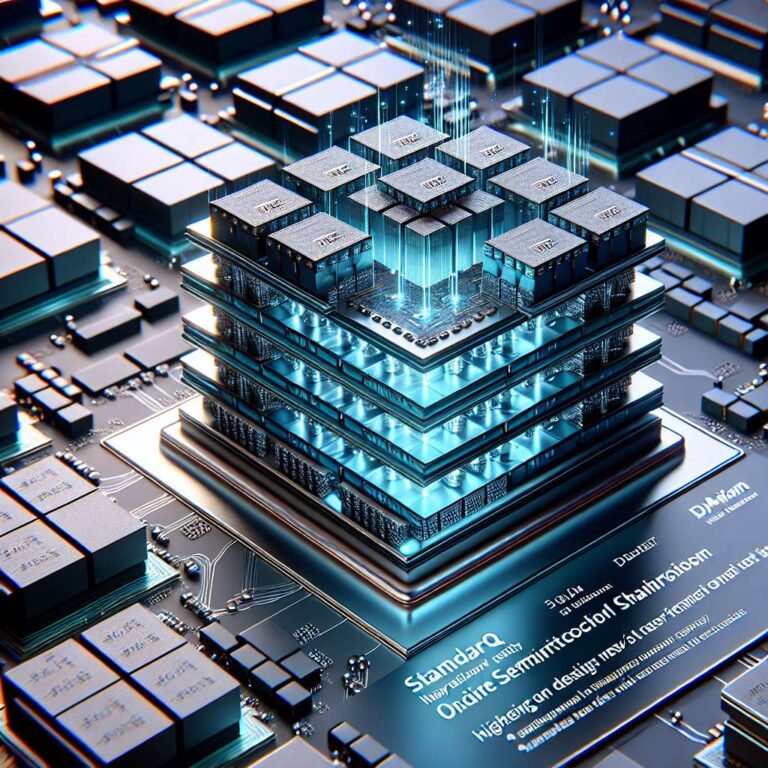

Kioxia Corporation announced that it has developed highly stackable oxide semiconductor channel transistors designed to make high density, low power 3D DRAM practical for commercial use. The company presented the technology at the IEEE International Electron Devices Meeting in San Francisco, USA, on December 10, positioning it as a way to cut power consumption in systems ranging from servers for Artificial Intelligence workloads to internet of things endpoints.

The company framed the work as a response to the era of Artificial Intelligence, in which demand is rising for DRAM that combines larger capacity with lower power draw in order to handle very large data sets efficiently. Traditional DRAM scaling is running into physical limits on how small memory cells can get, which has driven research into 3D stacking of memory cells as a path to further capacity gains without shrinking cells in two dimensions.

According to Kioxia, using single crystal silicon as the transistor channel material in stacked memory cells, as in conventional DRAM, both raises manufacturing costs and increases the power required to refresh memory cells in proportion to total memory capacity. The newly developed oxide semiconductor channel transistors are intended to address these constraints by enabling more easily stackable structures that help keep both cost and refresh power in check, supporting the practical implementation of denser, more energy efficient 3D DRAM devices for next generation computing applications.