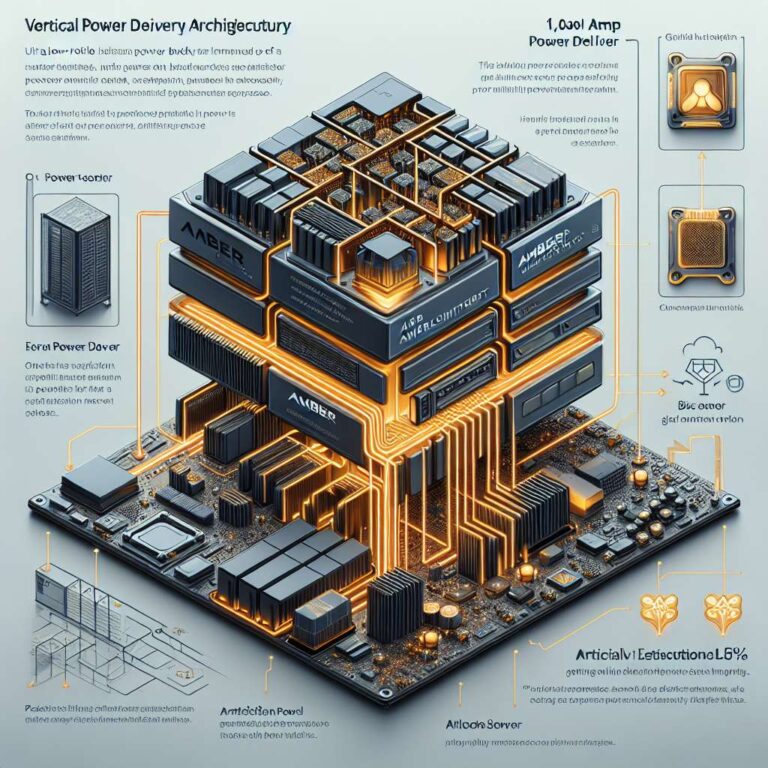

Amber Semiconductor, Inc., a fabless semiconductor company focused on next generation power management for data centers, has announced the successful tape out of its AmbersSemi Powertile vertical power delivery solution built specifically for artificial intelligence processors in data centers. The company positions Powertile as a new approach to feeding increasingly power hungry accelerators, with the device installed on the backside of a server board directly under the processor package rather than at the board periphery.

The ultra low profile Powertile is described as a 1,000 Amp vertical power device that can be mounted on the backside of a server board, directly beneath the processor. By pushing current through a short vertical path instead of across the board in a traditional lateral distribution layout, AmbersSemi states that Powertile reduces power distribution losses to the processor by more than 85%, which is intended to improve overall efficiency and make it easier to scale power delivery as artificial intelligence workloads grow.

Chief executive officer Thar Casey says the product represents a paradigm change in how power is distributed and delivered to artificial intelligence processors in data centers, arguing that existing architectures are struggling to keep up with the rising demands of next generation chips and are creating a performance limiting bottleneck. According to Casey, Powertile is designed to deliver extremely high current in a compact form factor that mounts directly beneath the processor for a shorter and more efficient power path, and the completion of this tape out is described as a critical inflection point as the company moves toward commercialization.