The NanoIC pilot line, a European initiative coordinated by imec and focused on innovation in chip technologies beyond 2 nm, has released two first of a kind advanced interconnect process design kits that target next generation chip to chip designs. The launch includes a fine pitch redistribution layer PDK and a die to wafer hybrid bonding PDK, both made available as early access offerings to accelerate development work across the semiconductor ecosystem.

These new PDKs are designed to bring advanced packaging capabilities within reach of universities, start ups, and established industry innovators that need to prototype and optimize complex multi die systems. By providing standardized design kits for fine pitch redistribution layers and die to wafer hybrid bonding, the NanoIC pilot line aims to reduce technical barriers and shorten development cycles for high density interconnect schemes that are essential for modern chiplet based architectures.

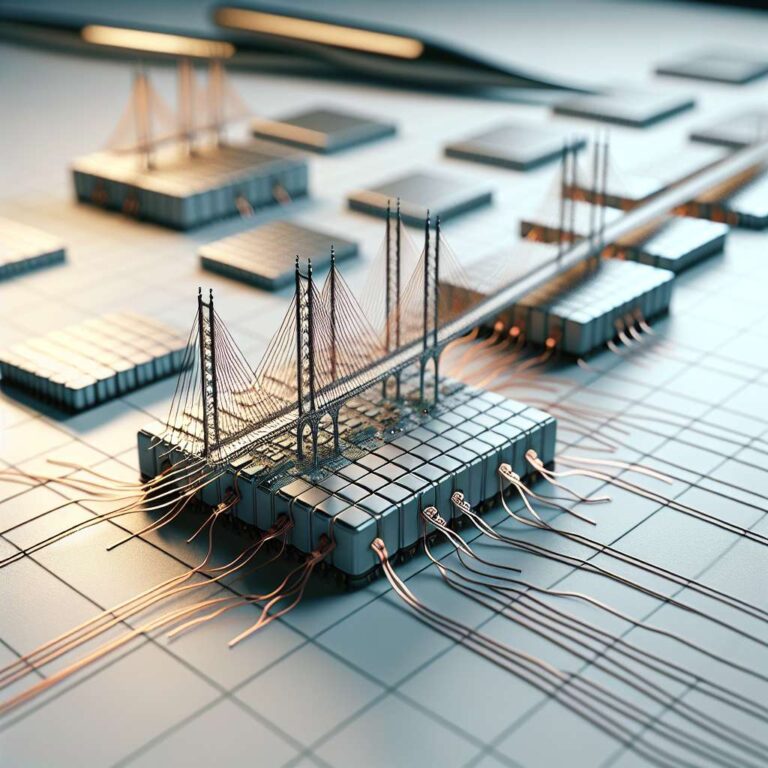

As system designs move toward more complex and heterogeneous architectures, advanced packaging has become critical to overall performance, energy efficiency, and bandwidth. Modern packaging no longer simply encloses single dies but instead tightly integrates multiple chiplets whose effectiveness depends on high quality interconnects. By enabling chiplets to be interconnected at high density, the NanoIC interconnect PDKs support the development of high performance computing platforms, Artificial Intelligence accelerators, and other data intensive applications that demand increasingly efficient chip to chip communication.