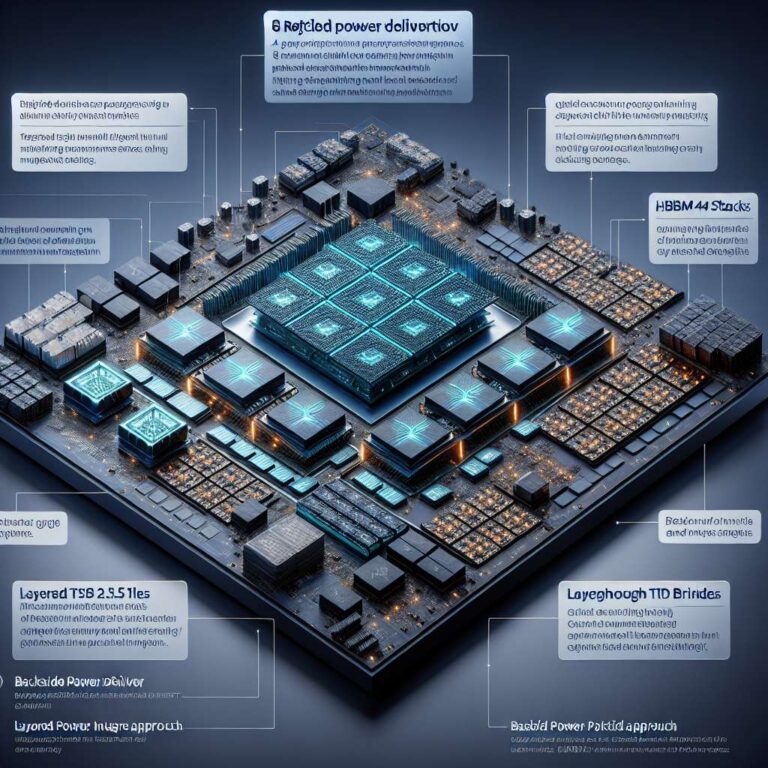

Intel Foundry has released a promotional document outlining its front-end and back-end technologies for artificial intelligence and high performance computing applications and has used it to showcase a new “artificial intelligence chip test vehicle” that demonstrates its current packaging capabilities. The test vehicle is an 8 reticle-sized system-in-package that features four logic tiles, 12 HBM4-class stacks, and two I/O tiles, and unlike a previous 16 logic tile and 24 HBM5 stack concept this configuration is described as manufacturable today. Intel emphasizes that this is not a working artificial intelligence accelerator, but a platform to show how future artificial intelligence and high performance computing processors can be physically assembled.

At the center of the design are four large logic tiles that are allegedly built on Intel 18A process technology with RibbonFET gate-all-around transistors and PowerVia backside power delivery, flanked by HBM4-class memory stacks and I/O tiles and connected via EMIB-T 2.5D bridges embedded directly in the package substrate. Intel uses EMIB-T, which adds through-silicon vias inside the bridges so that power and signals can pass vertically as well as laterally, to increase interconnect density and improve power delivery across the package. The platform is logically designed for UCIe die-to-die interfaces running at 32 GT/s and beyond, and these links are also described as being used to attach presumably C-HBM4E stacks for very high bandwidth memory access.

The test vehicle also illustrates Intel’s move toward greater vertical integration, with a roadmap that includes Intel 18A-PT process technology tailored for chiplets that stack other logic dies or memory on top and therefore require backside power delivery, pass-through TSVs, and hybrid bonding. In this design, 18A-PT base dies sit beneath 18A or 18A-P compute dies and can either act as large caches or perform additional compute work, and vertical connections are provided by the Foveros family of packaging technologies, including Foveros 2.5D, Foveros-R, and Foveros Direct 3D, to enable fine-pitch copper-to-copper bonding. For multi-chiplet artificial intelligence and high performance computing accelerators, Intel positions this hybrid lateral-and-vertical assembly, combined with EMIB bridges, as an alternative to large silicon interposers that can offer higher wafer utilization and yield, while a layered network of PowerVia, on-die Omni MIM capacitors, EMIB-T bridge-level decoupling, base-die eDTC and eMIM-T capacitors, and embedded CoaxMIL inductors is intended to support fast current swings of generative artificial intelligence workloads without collapsing voltage margins. Intel presents this artificial intelligence chip test vehicle as a tool to attract foundry customers, while leaving open whether its codenamed Jaguar Shores artificial intelligence accelerator, due in 2027, will directly adopt the showcased architecture.