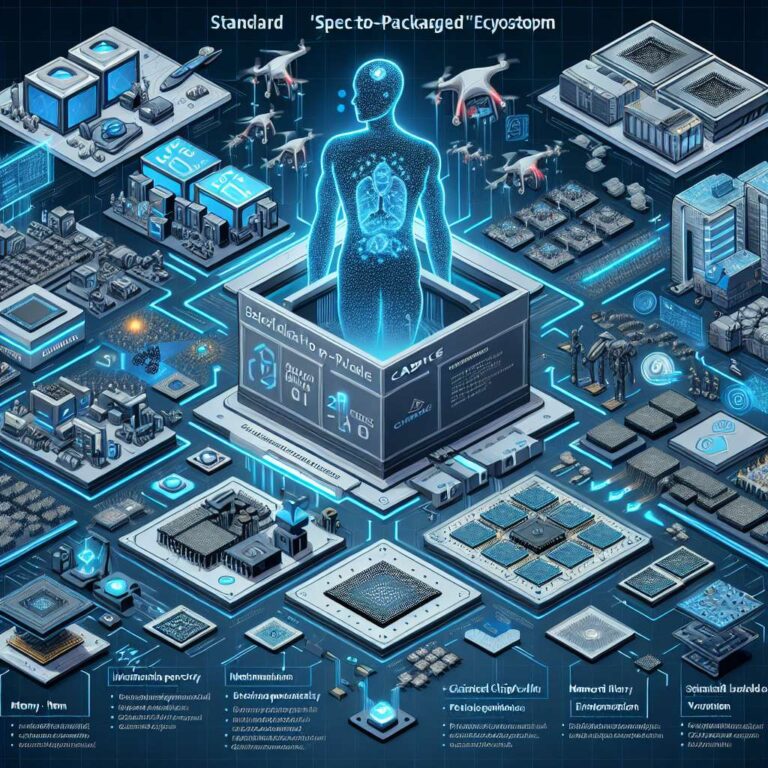

Cadence has unveiled a Chiplet Spec-to-Packaged Parts ecosystem designed to reduce engineering complexity and accelerate time to market for customers developing chiplets for physical artificial intelligence, data center and high performance computing applications. The initiative focuses on providing a cohesive environment that links specification through to packaged parts, so that customers can adopt chiplet based system designs without having to assemble and validate every piece on their own.

The ecosystem launches with a group of initial intellectual property partners that includes Arm, Arteris, eMemory, M31 Technology, Silicon Creations and Trilinear Technologies, along with silicon analytics partner proteanTecs. To further reduce risk and streamline customer adoption, Cadence is working with Samsung Foundry on a silicon prototype demonstration of the Cadence physical artificial intelligence chiplet platform that features pre integrated partner intellectual property built on the Samsung Foundry SF5A process. This prototype is intended to showcase how the ecosystem components can be combined in practical designs.

Cadence is also extending its longstanding collaboration with Arm to target both physical and infrastructure artificial intelligence workloads. Cadence plans to leverage the Arm Zena compute subsystem and other Arm intellectual property to enhance its physical artificial intelligence chiplet platform and its chiplet framework, so that the resulting solutions can handle next generation edge artificial intelligence processing for automobiles, robotics and drones while also supporting standards based I/O and memory chiplets for data center, cloud and high performance computing systems. Across these efforts, the company and its partners aim to cut engineering complexity, give customers a lower risk path to advanced chiplet adoption and help enable smarter, safer and more efficient electronic systems.